# Open-Source Design of a Low-Power SNN Hardware Accelerator for Edge AI

Luca Martis, Paolo Meloni

Dipartimento di Ingegneria Elettrica ed Elettronica, University of Cagliari, Italy

luca.martis@unica.it, paolo.meloni@unica.it

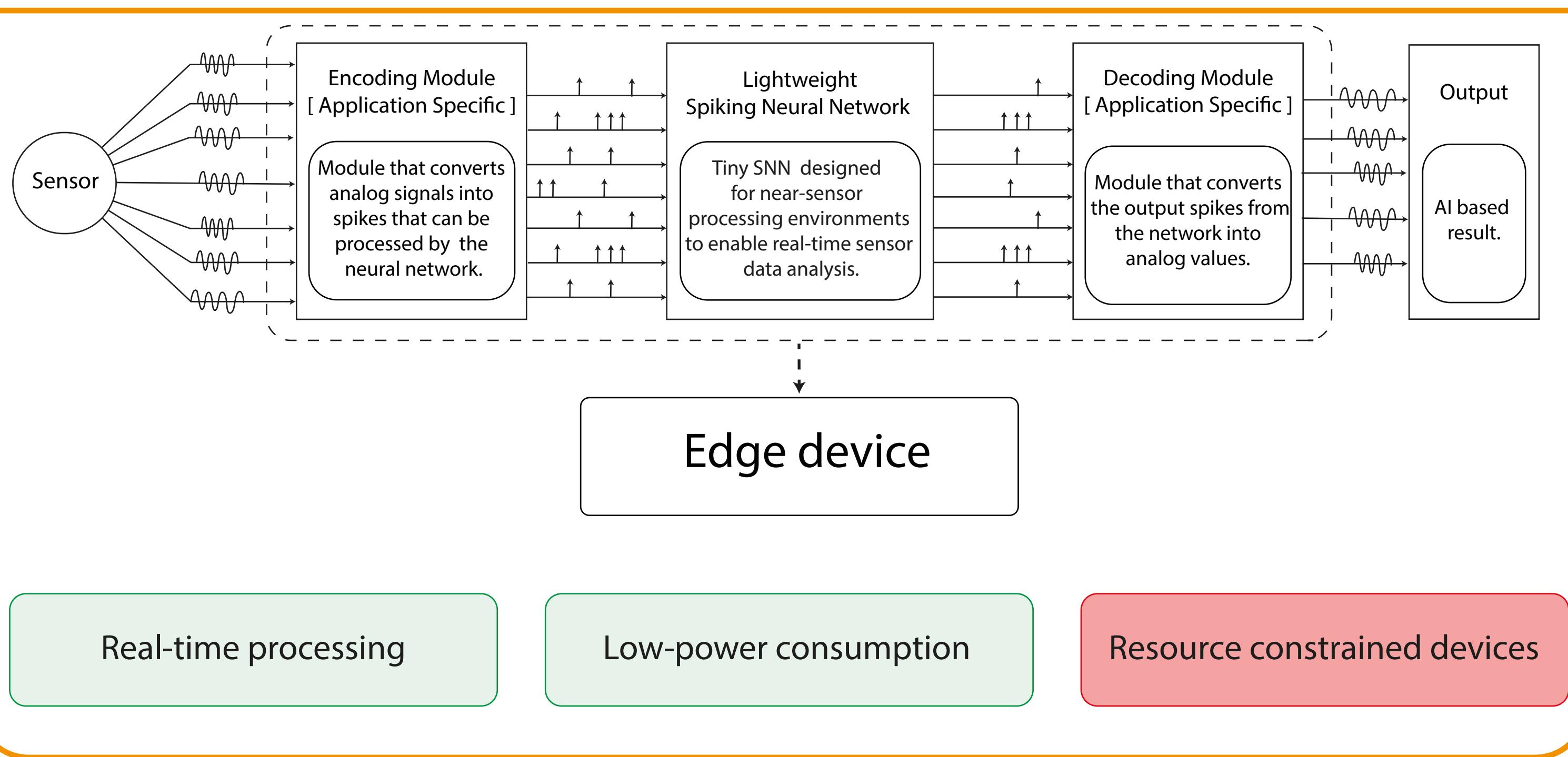

## Overview approach

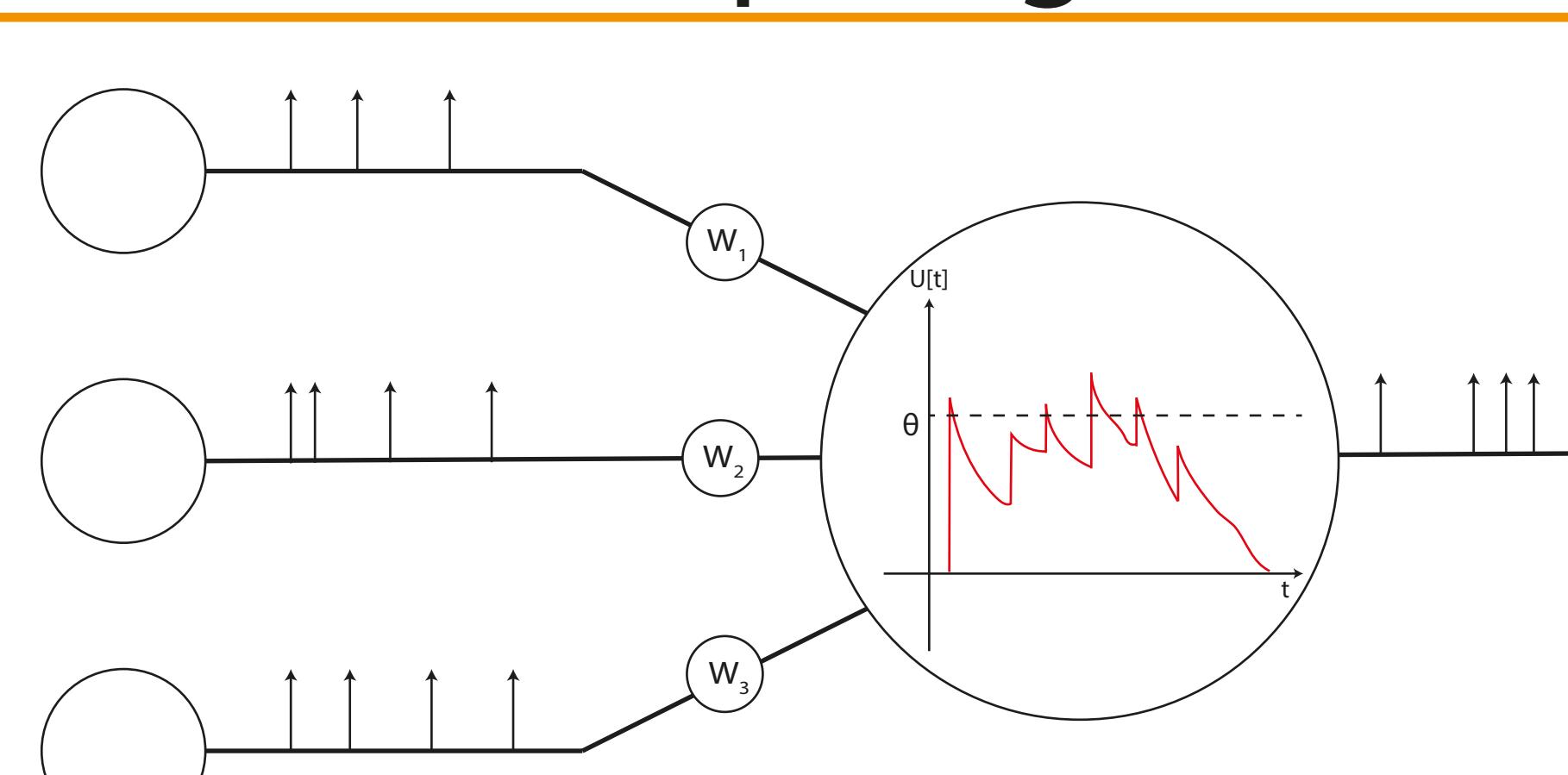

## Spiking Neural Network

Event-based processing.

Only accumulation operations are needed, thus reducing computational complexity.

Neuromorphic hardware limited by high development costs and restricted accessibility.

Spiking neural networks, considered as the third generation of neural networks, are characterized by neurons communicating via binary signals called spikes. This property makes them well-suited for edge devices, as it reduces computational complexity and enhances energy efficiency.

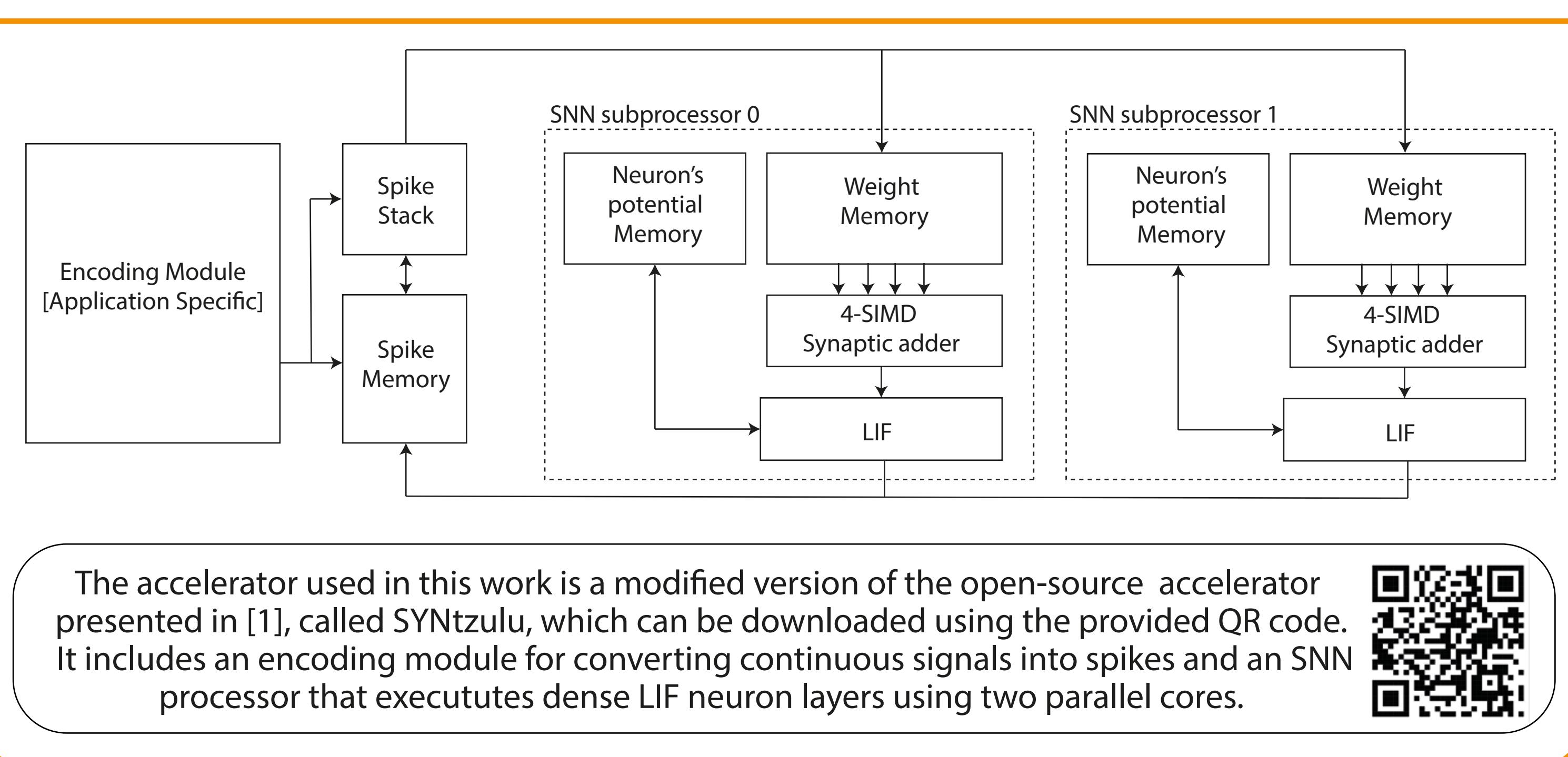

## SYNtzulu architecture

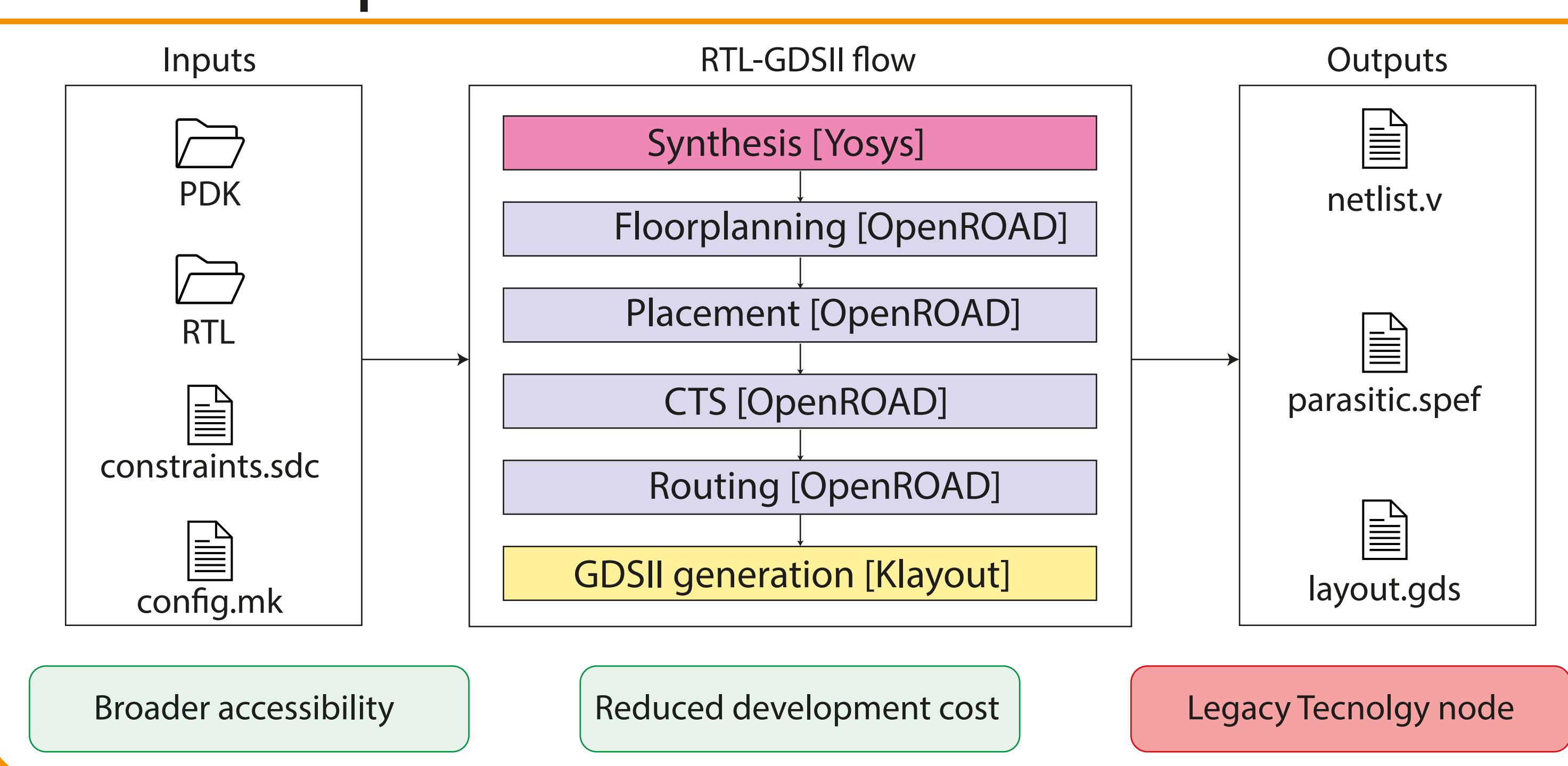

## Open-source RTL-GDSII flow

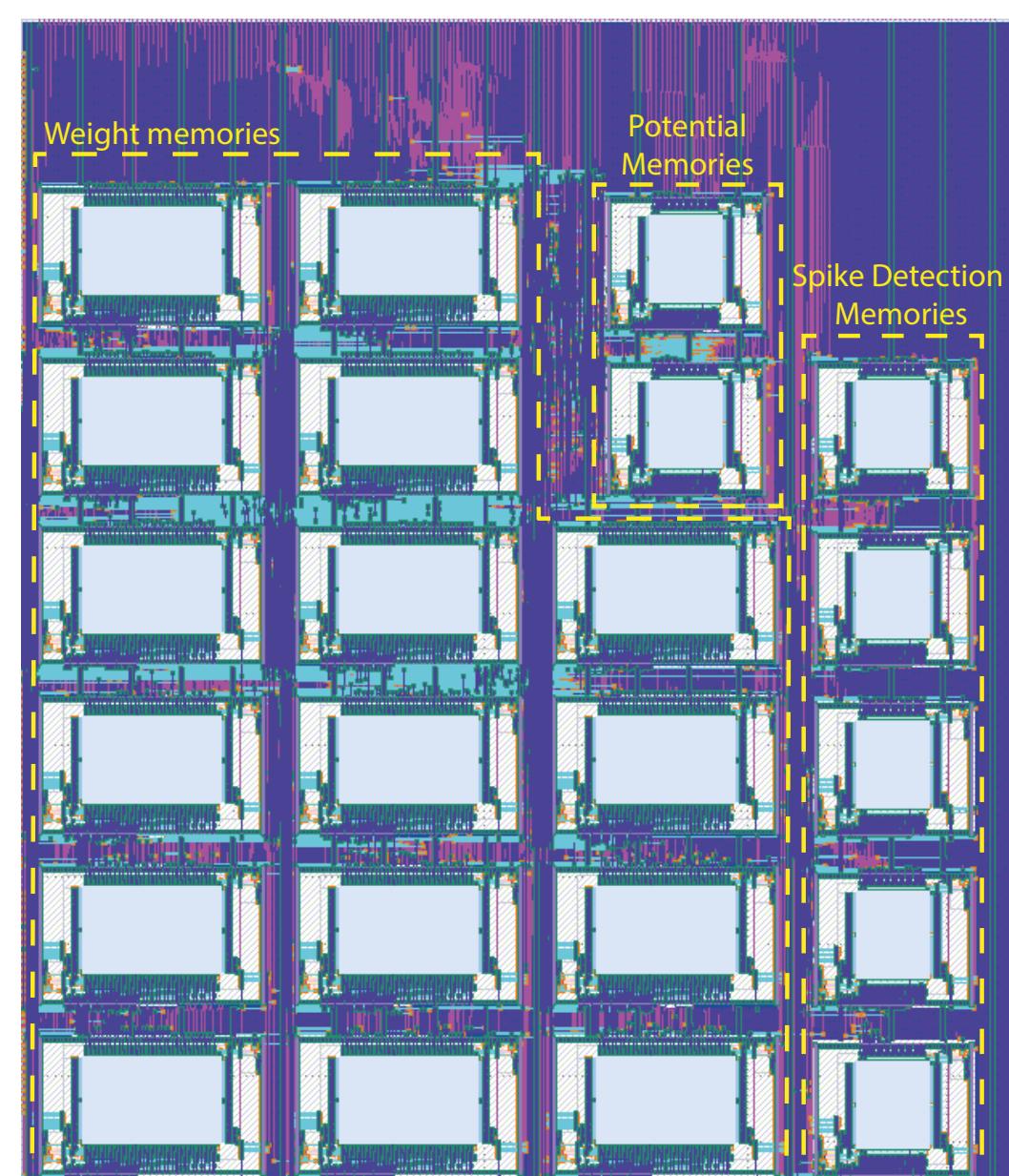

## HW accelerator with SKY130 PDK

|                       |                |

|-----------------------|----------------|

| Core Area             | 3000 x 3600 um |

| Standard Cells        | 8.922          |

| Max Neurons           | 512            |

| Max Synapses          | 32.768         |

| $F_{max}$             | 100 MHz        |

| Performance [100 MHz] | 0,8 GSOP/s     |

| $P_{inference}$       | 1,25 mW/MHz    |

| $P_{idle}$            | 350 $\mu$ W    |

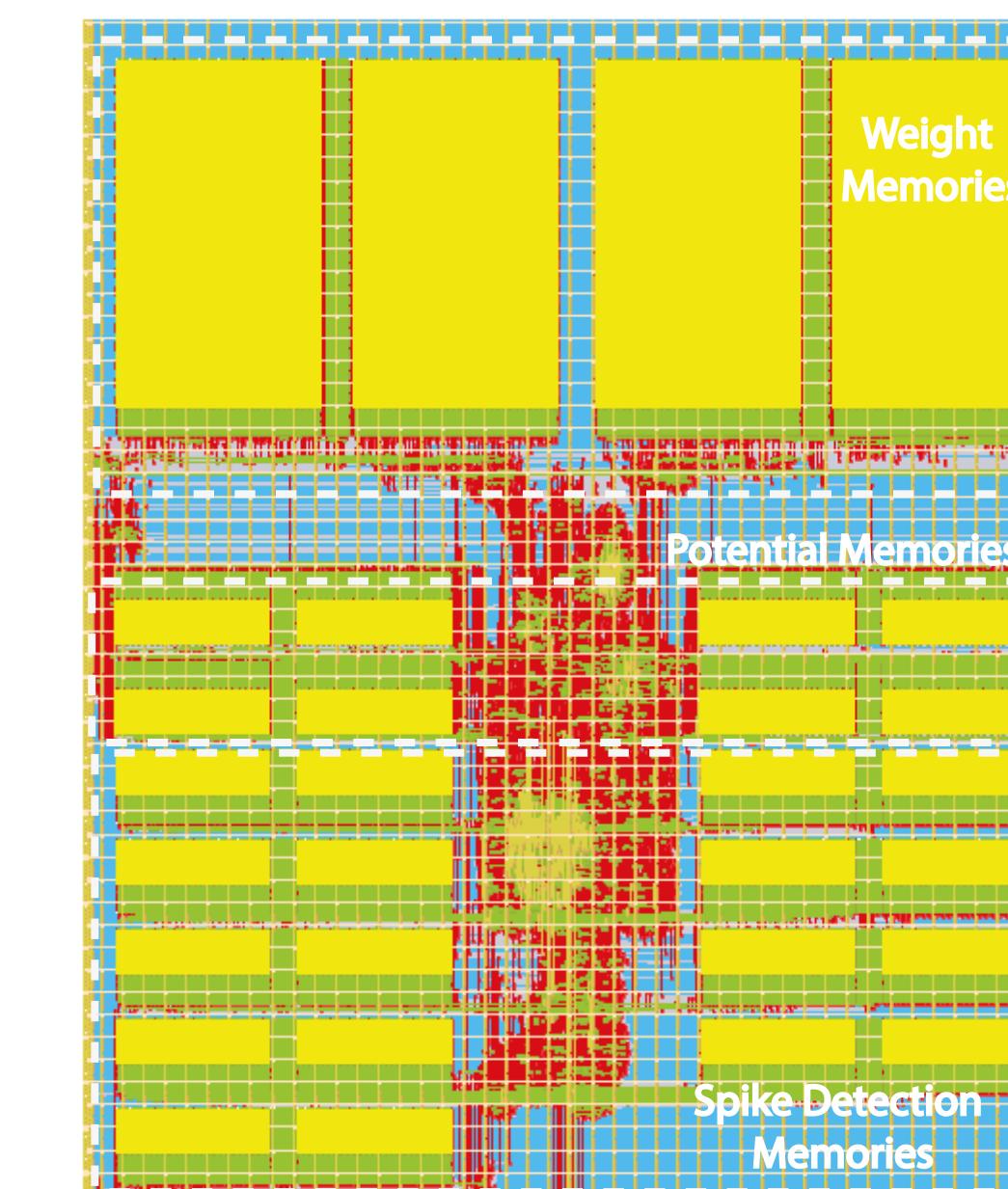

## HW accelerator with IHP-SG13G2 PDK

|                      |                |

|----------------------|----------------|

| Core Area            | 1750 x 2000 um |

| Standard Cells       | 15.725         |

| Max Neurons          | 512            |

| Max Synapses         | 32.768         |

| $F_{max}$            | 90 MHz         |

| Performance [90 MHz] | 0,72 GSOP/s    |

| $P_{inference}$      | 0,53 mW/MHz    |

| $P_{idle}$           | 81 $\mu$ W     |

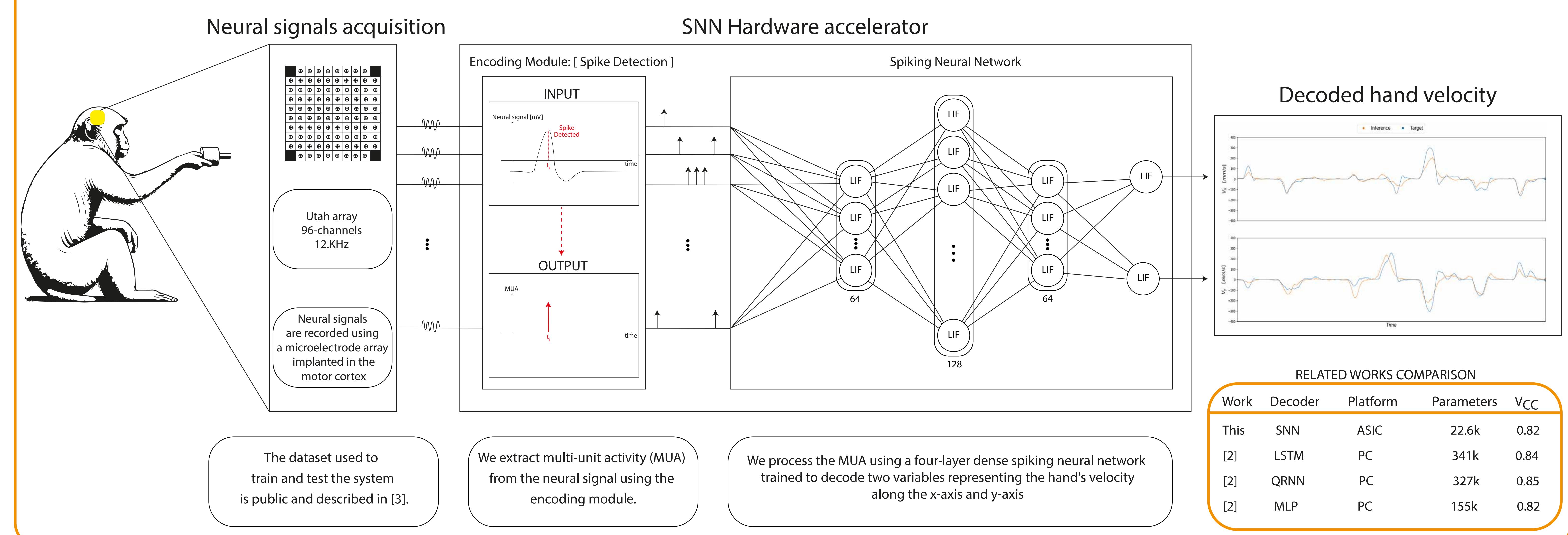

## Use case: Real time decoding of intracortical neural activity

### References

[1] G. Leone, M.-A. Scrigli, L. Badia, L. Martis, L. Ruffo and P. Meloni, "SYNtzulu: A Tiny RISC-V-Controlled SNN Processor for Real-Time Sensor Data Analysis on Low-Power FPGAs," in IEEE Transactions on Circuits and Systems I: Regular Papers.

[2] N. Ahmed, T. Adlou, A. Purwanti, T. G. Constantinou and C.-S. Bourguignon, "Improved Spike-Based Brain-Machine Interface Using Bayesian Adaptive Kernel Smoother and Deep Learning," in IEEE Access.

[3] L. O'Doherty, T. G. Constantinou, "Nonhuman primate reading with multichannel sensorimotor cortex electrophysiology," Zenodo, Sabes Lab, Univ. California, San Francisco, CA, USA, Tech. Rep, May 2020.

(Online Available: <https://doi.org/10.5281/zenodo.3854402>)

H2TRAIN project is supported by the Chips Joint Undertaking and its members, including the top-up funding by National Funding Authorities from Austria, Finland, Germany, Italy, Poland and Spain, under grant agreement no. 101140052. H2TRAIN project is supported by the Chips Joint Undertaking (GA 101140052) and its members including top-up funding by The National Funding Agency for Austria, The Innovation Funding Agency Business Finland, Bundesministerium für Bildung und Forschung, The Ministry of Universities and Research in Italy, The Ministry of Enterprises and Made in Italy, The National Centre for Research and Innovation in Poland, The Ministry for Digital Transformation and the Civil Service in Spain, and The State Research Agency in Spain.

This work was funded by H2TRAIN project, supported by the Chips Joint Undertaking (GA 101140052) and its members including top-up funding by The National Funding Agency for Austria, The Innovation Funding Agency Business Finland, Bundesministerium für Bildung und Forschung, The Ministry of Universities and Research in Italy, The Ministry of Enterprises and Made in Italy, The National Centre for Research and Innovation in Poland, The Ministry for Digital Transformation and the Civil Service in Spain, and The State Research Agency in Spain.

EUROPEAN

PARTNERSHIP

UNICA

UNIVERSITÀ DEGLI STUDI

DI CAGLIARI