29-3-9

# 2차 델타 시그마 변조기법을 이용한 고 정밀 및 고 안정 디지털 전자석 전원 장치에 관한 연구

(A Study on High Precision and High Stability Digital Magnet Power Supply Using Second Order Delta—Sigma modulation)

김금수\*·장길진·김동희

(Kum-Su Kim·Kil-Jin Jang·Dong-Hee Kim)

#### **Abstract**

This paper is writing about developing magnet power supply. It is very important for power supply to obtain output current in high precision and high stability. As a switching noise and a power noise are the cause of disrupting the stability of output current, to remove these at the front end, low pass filter with 300Hz cutoff frequency is designed and placed. And also to minimize switching noise of the current into magnet and to stop abrupt fluctuations, output filter should be designed, when doing this, we design it by considering load has high value inductance. As power supply demands the stability of less than 5ppm, high precision 24bit(300nV/bit) analog digital converter is needed. As resolving power of 24bit(300nV/bit) analog digital converter is high, it is also very important to design the input stage of analog digital converter. To remove input noise, 4th order low pass filter is composed. Due to the limitation of clock, to minimize quantization error between 15bit DPWM and output of ADC having 24bit resolving power,  $\Sigma - \Delta$  modulation is used and bit contracted DPWM is constituted. And before implementing, to maximize efficiency, simulink is used.

Key Words: Magnetic Power Supply, Delta-Sigma Modulation, Simulink, PID Control

# 1. 서 론

마그네트 파워 서플라이는 일정한 전류를 지속적으로 공급하여 전자석의 자속을 일정하게 유지할 수 있어야 한다. 따라서 시스템의 안정도가 매우 중요하고

\* Main author : Nuri Technology CEO Tel : 053-961-9001, Fax : 053-961-9005

E-mail: kgs@nuritec.co.kr Received: 2014. 12. 10 Accepted: 2015. 2. 2 외부(온도, 습도, 전원 등)의 변화 시에도 안정된 전류가 공급되어야 한다. 본 논문에서는 FPGA로 구성된 PI 제어기법과 클록의 한계로 인해 분해능이 15bit의디지털 PWM과 24bit의 분해능을 가진 아날로그 디지털 컨버터의 출력 사이에서 발생하는 양자화에러를 최소화하기 위해  $\Delta - \Sigma$  변조를 활용하여 bit축약이된 디지털 PWM을 구성하였다. 그리고 이에 필요한입출력 필터 및 ADC 입력 필터의 설계를 기술하고자한다.

본 연구의 목적은 안정된 시스템을 구현해 내는 것이다. 이를 위해 고 분해능의 아날로그 디지털 컨버터와 고 정밀 PWM을 통해 수 ppm의 전류안정도를 가지도록 설계하는 것이다.

본 연구는 고 정밀, 고 안정도 전자석전원장치의 구성과 특성 및 실험결과에 대하여 기술하였다. 그리고 제어시뮬레이션 소프트웨어인 simulink를 이용하여실제회로와 동일한 조건으로 모델링하여 실험 측정값과 시뮬레이션 결과 값을 비교·분석하여 최적의 결과를 도출해내었다.

# 2. 전자석 전원장치 구성

마그네트 파워 서플라이의 구성요건 중 첫 번째는 안정도이며, 10ppm 이하의 안정도를 실현하여야 한다. 그리고 두 번째는 마그네트 인덕턴스에 따른 전류의 상승속도를 실현 하여야 한다. 일반적인 마그네트의 인덕턴스가 25mH라고 가정하고,  $V=L\frac{di(t)}{dt}$ 이므로 V=32V, I=20A, L=25mH의 값을 대입하면,  $t=\frac{20*25*10^{-3}}{32}=15.625$ ms가 되고 시스템의 폐루프 응답특성은 최소 약 15.6ms 이하가 되어야한다. 따라서 시스템의 대역폭  $FB>\frac{1}{15.6*10^{-3}}=64$ Hz이다.  $FB=\frac{1}{15.6*10^{-3}}=64$ Hz이다.

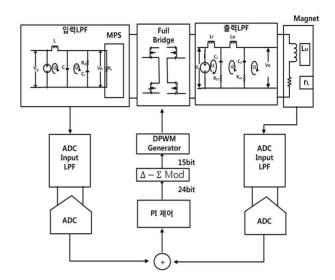

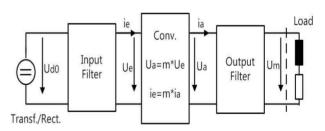

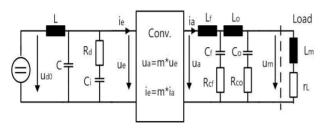

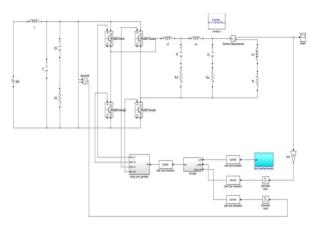

입력단의 전원 노이즈를 제거하기 위한 저역통과 필터와 전자석으로 들어가는 전류의 스위칭 noise를 줄이고 DC 입력속도의 갑작스러운 변동을 막기위해서 출력 필터를 추가하였다. 그리고 ADC의 높은 분해능 때문에 ADC 입력의 noise를 줄이기 위해서 ADC 입력단에 4차 저역 필터를 구성하였으며, 여기에 du/dt에 의해서 갑작스럽게 변하는 값으로부터 출력 필터를 보호하기 위해서 PI 제어기에 limiter를 추가하였고 ADC 출력과 DPWM에 의한 양자화에러를 최소화하기 위해  $\Delta - \Sigma$  변조를 활용하여 bit 축약을 하였다. 시스템의 전체 구성도는 그림 1과 같다.

그림 1. 전자석 전원장치 회로구성도 Fig. 1. The Magnet Power Supply Circuit Diagram

### 3. 필터설계

# 3.1 입력필터의 설계

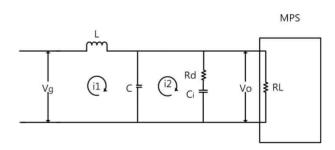

그림 2. 병렬 감쇠 필터의 기본회로 Fig. 2. The Basic Circuit of Shunt Attenuation Filter

기본회로에서  $R_L$ 이 충분히 크다고 가정하고 MESH 방정식을 적용하여 식 (1)과 같은 방정식을 얻을 수 있다.

$$\begin{pmatrix} V_g \\ 0 \end{pmatrix} = \begin{pmatrix} sL + \frac{1}{sC} & -\frac{1}{sC} \\ -\frac{1}{sC} & \frac{1}{sC} + R_d + \frac{1}{sC_i} \end{pmatrix} \begin{pmatrix} i_1 \\ i_2 \end{pmatrix}$$

(1)

$$V_o = (i_1 - i_2) \frac{1}{{}_{\rm S}C} \tag{2}$$

식 (1)과 식 (2)의 방정식을 줄여 정리하면 전달함수 인 식 (3)이 된다.

$$\frac{V_o}{V_g} = \frac{1 + s C_i R_d}{s^3 L C C_i R_d + s^2 L (C + C_i) + s C_i R_d + 1}$$

(3)

C¡R₀

시정수보다

높은

주파수영역대에서는

1+sC¡R₀

≒sC¡R₀

됨으로 식 (3)을 정리하여 2차계

의 전달함수인 H(s)로 줄일 수 있다.

$$H(s) = \frac{1}{LCs^2 + \frac{L(C + C_i)}{C_i R_d}} s + 1$$

(4)

식 (4)에서  $\frac{C_i}{C}$ =n로 놓으면 식 (5)가 된다.

$$H(s) = \frac{1}{LCs^2 + \frac{L}{R_d} \frac{n+1}{n} s + 1}$$

(5)

특성 방정식은

$$s^2 + \frac{1}{CR_d} \frac{(n+1)}{n} s + \frac{1}{LC} = 0$$

(6)

이며,  $s^2 + 2\xi\omega_n s + \omega_n^2 = 0$ 와 비교하면 식 (7)과 식 (8)이 된다.

$$\omega_n = \frac{1}{\sqrt{LC}} \tag{7}$$

$$\xi = \frac{n+1}{n} \frac{L}{2R_d \sqrt{LC}} \tag{8}$$

감쇠 회로의 최적조건( $\xi_{out}$ )은 식 (9)와 같다.

$$\xi_{opt} = \sqrt{\frac{(2+n)(4+3n)}{2n^2(4+n)}} \tag{9}$$

이를 이용한 최적 감쇠 저항값( $R_{dopt}$ )은  $C_i = 4C$ 일 때 식 (10)이 된다[14].

$$R_{dopt} = \sqrt{\frac{L}{C}} \frac{n+1}{2n} \sqrt{\frac{2n^2(4+n)}{(2+n)(4+3n)}} = \sqrt{\frac{L}{C}}$$

(10)

설계된 감쇠 회로의 C<sub>i</sub>, R<sub>d</sub>값의 선정은 SMPS피드 백 루프 대역폭의 약10배 정도인 3kHz를 f<sub>c</sub>로 잡고 계산한다면 L=150uH, C=170uF, C<sub>i</sub>는 C의 4배인 680uF 가 된다. 그리고 R<sub>dopt</sub>값을 구하기 위해서 식 (10)에 대입하여 계산을 하면

$$R_{dopt} = \sqrt{\frac{150*10^{-6}}{170*10^{-6}}} = 0.882[\Omega]$$

가 된다.

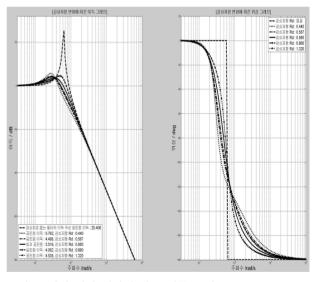

이 값과 비교하기 위해서 MATLAB 프로그램을 이용해 공진점 이득이 최저인 점을 찾기 위해서 식 (3)의 전달함수에 L, C, C,를 변경하여 감쇠 저항을 0.005씩  $1\Omega$ 에서  $2\Omega$ 까지 변경시켰다. 최적의 감쇠 저항값을 찾은 결과  $0.88\Omega$ 에서 공진점 이득이 3.519dB로 최저로 나타났다.

결론적으로 오차는  $0.002\Omega$ 로 근소하게 차이가 났다.

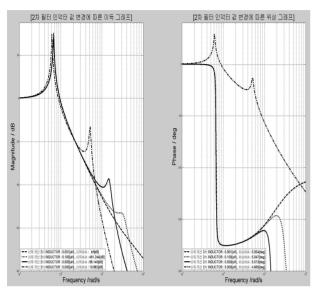

그림 3. 감쇠 저항 변화에 따른 이득 그래프 Fig. 3. A Graph of a Gain According to a Change of Attenuation Resister

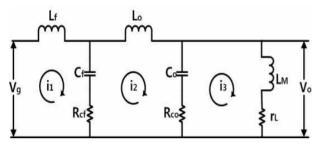

# 3.2 출력필터 및 전자석 부하 모델링

출력 필터의 설계에서 시스템의 주파수 대역폭이 300Hz이고 출력에 인덕턴스 부하가 구성된 점을 고려

하여 차단주파수가 1kHz인 출력 필터를 구성하였다. 2차 저역 필터를 활용하고 출력 필터의 차단주파수가 1kHz가 되게 설정하기 위해 감쇠 저항값을 조정함으로써, 필터의 효율을 높이는 작업을 수행하였다. 설계된 전자석 전원 장치의 출력 부분의 등가 모델을 그림 4와 같이 정의하였으며, 이것의 전달함수는 MESH 방정식을 세워 줄 수 있다.

그림 4. 출력 필터 및 전자석 모델링 Fig. 4. A Modelling of a Output Filter And Magnet

여기에서  $Z_{fc}=\frac{1}{s\,C_f}+R_{cf},~Z_{oc}=\frac{1}{s\,C_o}+R_{co}$ 라고 하면 은 식 (11)과 같이 나온다.

$$\begin{pmatrix} V_g \\ 0 \\ 0 \end{pmatrix} = \begin{pmatrix} sL_f + Z_{fc} & -Z_{fc} & 0 \\ -Z_{fc} & Z_{fc} + sL_o + Z_{oc} & -Z_{oc} \\ 0 & -Z_{oc} & Z_{oc} + sL_M + r_L \end{pmatrix} \begin{pmatrix} i_1 \\ i_2 \\ i_3 \end{pmatrix}$$

$$(11)$$

출력 필터의 출력인

$$V_o = i_3(sL_M + r_L)$$

(12)

전달함수는

$$H(s) = \frac{V_o(s)}{V_q(s)}$$

이고 (13)

식 (11)과 식 (12)를 정리하면 식 (14)와 같다.

$$H(s) = \frac{C_o L_M R_{oo} s^2 + (L_M + C_o R_{oo} r_L) s + r_L}{U s^5 + V s^4 + W s^3 + X s^2 + Y s + Z}$$

(14)

여기서

$$\begin{split} &U = CL_fL_ML_o\\ &V = C_fC_oL_fL_MR_{cf} + C_fC_oL_fL_MR_{co} + C_fC_oLL_oR_{co}\\ &+ C_fC_oL_ML_oR_c + C_fC_oL_ML_or_L \end{split}$$

$W=C_fL_fL_M+C_fL_fL_o+C_oL_fL_M+C_oL_ML_o+C_fC_oL_fR_{co}r_L$

$X = C_f r_L L_f + C_o L_f R_{co} + C_o r_L L_f + C_o L_M R_{co} + C_o L_o R_{co} + C_o L_o r_L$

$Y=L_f+L_o+L_m+C_oR_{co}r_L$

Z=ri이다.

Le은 1차 필터의 인덕턴스, Ce는 1차 필터의 커패시 터, Lo는 2차 필터의 인덕턴스, Co는 2차 필터의 커패 시터, rr은 전자석 동선의 DC저항, Lm은 전자석의 인 덕턴스이다. Lm이 유도성인 것을 고려하여 필터의 1차 공진주파수를 1kHz로 설정하기 위해 MATLAB 프로그램을 이용해 식 (14)에 값을 대입하여 L=20uH, C=100uF, C<sub>0</sub>=1000uF, L<sub>M</sub>=20mH로 값을 정하고 2차 필터의 인덕턴스인 L。를 0.001uH에서 5uH까지 변경 시켜 2차 공진주파수를 변경하여 LFP의 특성을 개선 하려고 모의실험을 하였으나 그림 5와 같이 위상 여유 가 4deg로 낮고 1, 2차 공진점의 Q값이 너무 커서 시 스템의 불안한 요소가 많았다. 그래서 감쇠 저항 0.50 을 추가하여 실험한 결과 그림 6과 같은 결과를 얻었 다. 그림에서 보는 바와 같이 위상 여유도가 4deg에서 76deg로 개선되었고 차단주파수 이하에서 이득 또한 평탄하게 좋아진 것을 볼 수 있다.

그림 5는 전자석 전원 장치의 2차 필터의 인덕턴스 값에 따른 주파수 감쇠 특성을 나타내고 있다. 그림 6에서 알 수 있듯이 감쇠 저항을 추가했을 때 파형이더 완만한 것을 알 수 있었다.

#### 3.3 ADC 입력 필터

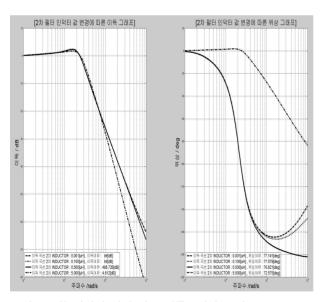

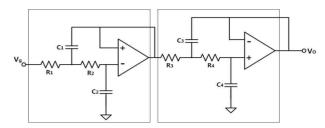

24bit ADC를 사용하기 때문에 300nV/bit의 분해능을 가지고 있어서 입력에서 작은 noise 영향에도 출력 안정도에 영향을 미친다. 따라서 ADC 입력에 적절한 저역통과필터가 필요하고 이것은 시스템 성능에 직접적인 영향을 주므로 상당히 중요한 요소이다. 본 시스템에서는 4차 저역 필터를 그림 7과 같이 구성하였고 ADC의 sampling 주파수가 128kHz이고 시스템 폐루

프 대역폭이 300Hz이므로 sampling 주파수의 약 1/12 인 10kHz을 차단주파수로 잡았다.

그림 5. 2차 인덕터 값에 따른 이득·위상 그래프 (R<sub>d</sub>가 ESR이 0.05Ω인 경우)

Fig. 5. A Graph of Gain And Phase According to Second Filter's Inductor Value. (In Case That ESR of Rcf is  $0.005\Omega$

그림 6. 2차 인덕터 값에 따른 이득·위상 그래프 (R<sub>ơ</sub>가 0.5Ω의 감쇠 저항으로 계산)

Fig. 6. A Graph of Gain and Phase According to Second Filter's Inductor Value( $R_{cf}$  is  $0.5\Omega$  Attenuation Resistor

그림 7. 이득이 1인 4차 저역통과필터 Fig. 7. Fourth Order Low Pass Filter whose Gain is 1

이때 출력전압의 레귤레이션의 오차를 줄이기 위해서는 DC에서의 이득이 평탄해야 하므로 위의 그림 7에서 보는 바와 같이 2차의 Sallen Key 저역통과필터를 직렬로 결합하여 4차의 필터를 구성하고 최적의 필터 효과를 내기 위해 다음과 같은 분석 작업을 수행하였다.

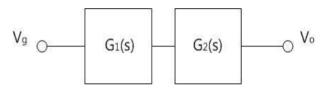

$$G(s)=G_1(s)G_2(s)$$

(15)

그림 8. 이득이 1인 4차 저역통과필터 전달함수 Fig. 8. The Transfer Function of 4th Order Low Pass Filter Whose Gain is 1

전달함수는 방정식을 세워 구할 수 있다. 이득이 1인 필터 회로로 구성된 그림 7에서 전달함수를 구하면 식 (16)과 같다.

$$G(s) = \frac{A}{(1 + a_1 s + b_1 s^2)(1 + a_2 s + b_2 s^2)}$$

(16)

식 (16)에서  $a_1=(R_1+R_2)\,C_1$  , $b_1=C_1C_2R_1R_2$ ,  $a_2=(R_3+R_4)\,C_3$  , $b_2=C_3C_4R_3R_4$  이다. 그리고 A=1 이 면,  $R_1$ 과  $R_2$ 를 식 (17)과 식 (18)과 같이 나타낼 수 있고,  $R_3$ ,  $R_4$ 도 마찬가지의 방식으로 유도될 수 있다[15].

$$R_1 = \frac{a_1 C_1 - \sqrt{a_1^2 C_2^2 - 4b_1 C_1 C_2}}{4\pi f_c C_1 C_2} \tag{17}$$

$$R_2 = \frac{a_1 C_1 + \sqrt{a_1^2 C_2^2 - 4b_1 C_1 C_2}}{4\pi f_c C_1 C_2} \tag{18}$$

저항 값 R₁과 R₂는 식 (19)를 통해서 계산된다.

$$R_{1,2} = \frac{a_1 C_2 \mp \sqrt{a_1^2 C_2^2 - 4b_1 C_1 C_2}}{4\pi f_c C_1 C_2}$$

(19)

위의 식에서 실수의 값을 가지기 위한  $C_2$ 의 조건은 식 (20)과 같다.

$$C_2 \ge C_1 \frac{4b_1}{a_1^2} \tag{20}$$

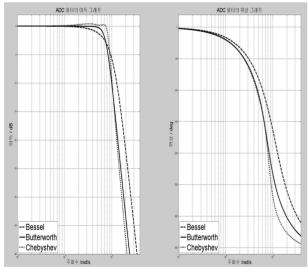

차단주파수  $f_c$ =10kHz로 설정하고 MATLAB을 이용하여 Bessel, Butterworth, chebyshev에 4차 필터의 계수를 넣어 식 (16)에 대입하여 그림 9에서와 같이 이득과 위상그래프로 나타내었다.  $C_1$ =1.1nF,  $C_2$ =910pF,  $C_3$ =6.8nF,  $C_4$ =910pF,  $R_1$ =11.3k $\Omega$ ,  $R_2$ =15.4k $\Omega$ ,  $R_3$ =3.83k $\Omega$ ,  $R_4$ =7.15k $\Omega$ 이다[15].

마그네트 파워 서플라이는 안정된 전류를 공급해야 되므로 그림 9에서 볼 때 평탄특성과 차단특성이 셋 중에 비교적 좋은 Butterworth 저역통과필터를 사용 하였다.

그림 9. ADC 필터의 이득 및 위상그래프 Fig. 9. A Graph of The Gain and Phase of ADC Filter

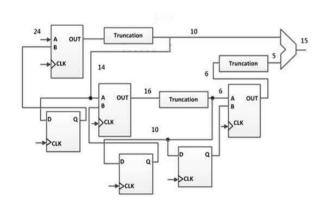

# 4. DPWM 비트 축약

PWM 컨트롤러가 50kHz DPWM에서 15bit의 분해 능을 가지고 있어 ADC 24bit의 신호와 차이가 생기고 이에 따라 발생하는 양자화 노이즈를 효율적으로 제거하기 위해서 MASH  $\Delta - \Sigma$  변조기를 사용 하였다.

# 4.1 MASH $\Delta - \Sigma$ 변조기의 설계

MASH  $\Delta - \Sigma$  변조기의 기본개념은 다음과 같다.

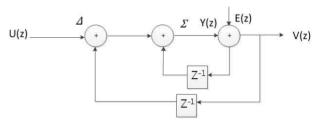

그림 10. First order  $\Delta$ - $\Sigma$  변조기 Fig. 10. !st Order  $\Delta$ - $\Sigma$  Modulator

위의 Block Diagram을 수식으로 정리하면 다음과 같다.

$$Y(z)=z^{-1}Y(z)+U(z)-z^{-1}V(z)$$

(21)

출력 V(z)는 V(z)=Y(z)+E(z)이므로 식 (21)에 대입하여 정리하면 식 (22)가 된다.

$$V(z)=z^{-1}Y(z)+U(z)-z^{-1}V(z)+E(z)$$

$$=U(z)+z^{-1}[Y(z)-V(z)]+E(z)$$

(22)

Y(z)-V(z)=-E(z)이므로 V(z)는 식 (23)과 같다.

$$V(z)=U(z)+(1-z^{-1})E(z)$$

(23)

DSP의 일반적인 형태의 수식은

$$V(z)=STF(z)U(z)+NTF(z)E(z)$$

(24)

로 나타낼 수 있으며, 식 (23)과 식 (24)를 비교하면 신

호전달함수 STF(z)=1, 노이즈 전달함수 NTF(z)=  $1-z^{-1}$ 임을 알 수 있다.

정상상태에서 z≒1이므로 ||NTF(z)||<<1이고 V(z) ≒U(z)가 된다[6].

따라서 외란(Noise) E(z)가 제거됨을 알 수 있다.

### 4.2 양자화 오차의 개선

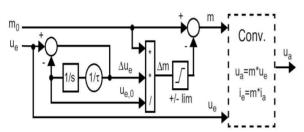

ADC출력이 24bit이고 피드백 된 제어 값 또한 24bit 라고 할 때, DPWM 분해능은 15bit이기 때문에 양자화에러를 발생시킨다. 양자화에러를 최소화시킬 필요가 있으므로  $\Delta - \Sigma$  변조를 활용하여 최소화 한다. 다음 그림 11은 Second-order  $\Delta - \Sigma$  변조를 활용한 bit 축약 Block Diagram이다.  $\Delta - \Sigma$  DPWM은 다음과 같다. 듀티값 d가 디지털 제어 법칙에 의해서 24bit로 생성된다.

그림 11. Second-Order Δ-Σ 변조를 활용한 bit 축약 Block Diagram

Fig. 11. Bit Contraction Block Diagra Using Second-Order  $\Delta$ - $\Sigma$  Modulator

# 5. PI 제어기 설계

PI 제어기의 계수는 증명이 되어있는 방식에 따라 결정된다. 모든 파워 서플라이 중에서 선형모델을 유도하고, 이 모델로부터 개방루프 주파수 응답이 모의실험 된다. Bode의 규칙에 따라서 P-계수, I-계수가 여러 동작점을 통해 정해진다.

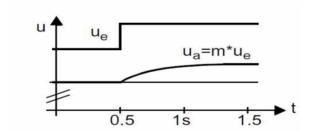

#### 5.1 DC전압 피드 포워드

DC 입력전압의 변동은 컨버터의 출력 전압의 변동을 초래한다. 즉 이것은 부하 전류의 변동을 일으킨다. 그렇지만 이것은 제어기에 의해 교정되어질 수 있다. 하지만 이때 시간차가 발생하게 된다. 중간 속도의 전압 변동은 매우 중요하고 빠른 펄스는 출력 필터에 의해 필터링 되고, 반면에 느린 펄스는 제어 루프에 의해서 쉽게 고쳐진다. 적절한 전압 피드 포워드로컨버터 출력에 있어서의 dc 전압 펄스화의 영향은 줄여질 수 있다. 식 (25)에서는 컨버터의 전달함수에 기반 해서 일정한 출력 전압에 대해 결과물 m\*ue가 일정해야한다.

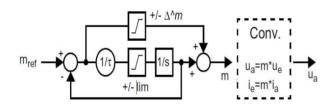

그림 12. 입·출력필터와 시간 연속적인 converter 모델 Block Diagram

Fig. 12. A Input And Output Filter And A Time Continuous Converter Model Block Diagram

$$u_a = m * u_e; i_e = m * i_a (-1 \le m \le 1)$$

(25)

$u_e$ 의 변화는 m의 적절한 변화로 보상되어야 한다. 출력 전압에 대해서 선형화된 식 (25)와 식 (26)을 통해서 식 (27)에서  $\Delta u_e$ 에 대해서 피드 포워드 계수가 유도될 수 있다.

$$\Delta u_a = m_0 \Delta u_e + \Delta m u_{e,0} = 0 \tag{26}$$

$$\Delta m = (-m_0/u_{e,0})\Delta u_e \tag{27}$$

연산을 해서 실행한 것을 그림 13에서 볼 수 있다. 저역통과 필터를 써서 미분을 하고 적분 시정수의 출력전압이 보상 안 된 늦은 변화는 전류 제어기로 보상할 수 있다. 이러한 피드 포워드 함수의 큰 영향은  $\Delta m$ 에 의해 제한시킬 수 있다. 이러한 일은 시작단계에서는 언제나 필요한 일이다.

(a)  $\Delta u_{ij}$ 에 대한 도함수를 포함하는 전압 피드 포워드의 Block Diagram

(b) m0가 대략 0.9인 경우에 전압의 피드 포워드를 포함하는 u<sub>e</sub>에 대한 함수 u<sub>a</sub>

그림 13. 피드 포워드의 Block Diagram과 그래프 Fig. 13. Block Diagram And Its Graph of Feedforward

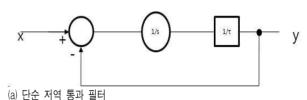

# 5.2 ADC 저역 필터 및 di/dt limiter

ADC를 통해 측정된 값에 대해서 간단한 저역 통과 필터에 DSP를 써서 그림 14 (a)에 나타내었다. 식 (28)은 일반적인 전달 함수이다. 여기서  $\tau$ 는 시 정수이다.

$$Y/X = 1/(s\tau + 1) \tag{28}$$

전자석 전원장치의 정격전압은 부하전류의 최대

di/dt에 의해 설계되어진다. 따라서 상기 기준 값에 대한 제한이 필요하다. 이 제한은 그림 14 (b)에서 그려진 것과 같이 저역 통과 필터와 결합되어있다.

최대출력의 상, 하한 값은 dy/dt를 결정한다. 입력부 분에서 limiter로 출력 y의 범위를 제한하도록 구현시 켰다.

(a) Simple Low Pass Filter

- (b) 최대 d/dt limiter를 가진 조합

- (b) Low Pass Filter Combination with Maximum d/dt limiter

그림 14. 저역통과필터 Fig. 14. Low Pass Filter

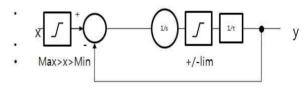

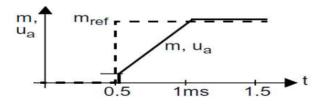

#### 5.3 dm/dt limiter

그림 15의 출력 필터에서 감쇠저항 R<sub>∞</sub>는 과전류로 손상을 입을 수 있다. 최악의 경우를 고려해보면 두 가지를 제한해야하는 것을 알 수 있다. 만약 모든 필터 요소가 생략되면, 저항을 통과하는 전류는 낮은 주 파수에서 iR<sub>∞</sub>≒C<sub>o</sub>du<sub>m</sub>/dt 가 된다. 만약 마그네트 전압이 최대 du/dt 로 진동하면, 저항을 통과하는 구형파의 전류가 발생한다. 주어진 전력 감쇠(P<sub>V</sub>)에 대해서최대 du<sub>m</sub>/d<sub>v</sub>는 식 (31)로 주어진다[15].

$$Pv = R_{co} I R_{co}^{2}$$

(29)

$$I_{Roo} = C_o \frac{du_m}{dt} \tag{30}$$

$$\frac{du_m}{dt} = \sqrt{\frac{PV}{R_{co}}} \frac{1}{C_o} = \frac{dm}{dt} u_e \tag{31}$$

76

고주파수에서 커패시터 C<sub>o</sub>는 무시될 수 있고, 마그 네트 전압은 감쇠저항에 걸리는 전압과 동일하다. 따라서 소멸된 전력에 대한 기여성분은 컨버터의 출력 전압에 의해서 제한될 수 있다.

그림 15. 입력 필터와 출력 필터의 시간 연속 변환 모델 및 전자석 전원 장치 구조

Fig. 15. Time Continuous Model And Magnet Power Supply Structure of Input Filter And Output Filter

손실이 두 현상사이에서 정확하게 나누어진다. 필터는 계산된 값들을 한층 더 감소시킬 것이다. 상하부의 값을 제한시키는 함수를 사용해서 그림 16 (a)와 같이 나타낼 수 있다. 위와 같은 사항들을 고려해서 다음과 같이 simulink model을 만들었다[15].

(a) 출력필터에서 감쇠저항에서 있을 수 있는 손실을 제한하는 소신호 바이패스를 가지는 dm/dt-limiter (b) dm/dt-Limiter with Small Signal Bypass That Limit Possible Loss In The Output Filter

(b) (a) 블록의 전달함수에 대한 그래프 (b) A Graph of Transfer Function of Block Diagram in (a)

그림 16. 출력필터의 Block Diagram과 그래프 Fig. 16. The Block Diagram And The Graph of Output Filter

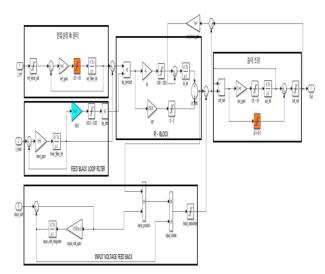

그림 17. 제어기의 완전한 simulink Block Diagram Fig. 17. A Complete Simulink Block Diagram of The Controller

# 5.4 시뮬레이션 결과 및 실험 결과

그림 18. 이산시간 Simulink Model Fig. 18. A Discrete time Simulink Model

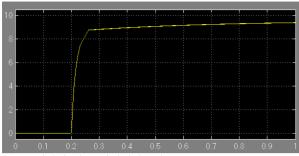

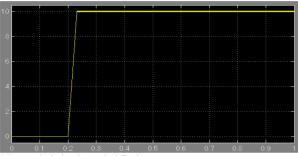

그림 18과 같이 PI 제어기를 simulink에서 Discrete-time 모델을 구성하여 3가지 항목에 대해 모의실험을 하였다. 그 결과 과도응답에 대해 제어기를 사용하지 않은 응답(그림 19 (a))에서는 목표 값(10A)에 도달하지 못하였다. (10초 이내) 그리고 상승시간 또한 늦어졌음을 보여준다.

앞에서 설계된 PI 제어기를 사용한 시뮬레이션결과 그림 19 (b)에서는 상승시간 20ms 이하를 유지

- (a) PI 제어기 없는 단위계단응답

- (a) A Unit Step Response Without PI Controller

- (b) PI 제어기 있는 단위응답

- (b) A Unit Step Response With PI Controller

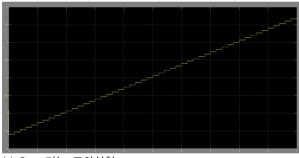

- (c) Step 기능 모의실험

- (c) A Step Function Simulation

그림 19. 단위응답과 Step 기능 모의실험 Fig. 19. Unit Step Responses And A Step function Simulation

표 1.  $\Delta - \Sigma$  변조 적용 전  $\cdot$  후 출력안정도 비교표 Table 1. Output Stability Comparison Before And After  $\Delta - \Sigma$  Modulation Application

|                | Δ-Σ 변조<br>적용 전 | Δ-Σ 변조<br>적용 후 |

|----------------|----------------|----------------|

| 리플률(r)         | 3.63ppm        | 1.38ppm        |

| 최대변동폭<br>(10A) | 224uA          | 112uA          |

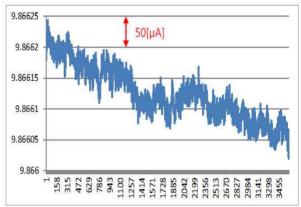

- (a) 10A 1h일 때,  $\Delta-\varSigma$  변조 적용 전 출력그래프

- (a) When 1h at 10A, The Output Graph Before Applying the  $\varDelta-\varSigma$  Modulation

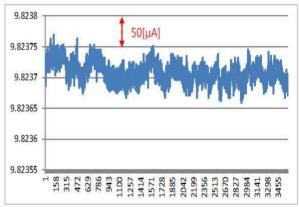

- (b) 10A 1h일 때,  $\Delta-\Sigma$  변조 적용 후 출력그래프

- (b) When 1h at 10A, The Output Graph After applying the  $\varDelta-\varSigma$  Modulation

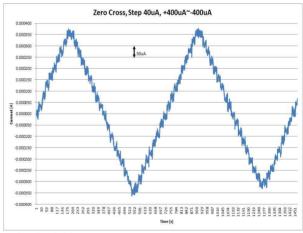

- (c) 영(O)통과 스텝 안정도

- (c) The Step Stability at Zero Pass

그림 20. 결과파형 Fig. 20. The Output WaveForm

하였고 정확하게 목표 값에 도달함을 보여준다. 또한 P-gain값과 I-gain값을 조정함으로써 목표 값의 상승시간을 조절할 수 있었으며 부하의 인덕턴스 값이 변경되더라도 PI-gain을 조정하여 안정도를 확보할 수 있었다.

# 6. 결 론

디지털 제어 전자석 전원 장치를 5ppm 이하 수준의 안정도를 구현하는데 있어서 FPGA에 PI 제어 Logic을 구현하기에 앞서 simulink로 모델을 만든 다음 이 것을 FPGA에 Logic으로 구현하였고, Bipolar전원으로 구현하는데 있어서 0A에 근접한 영역인 ±200uA의 영역에서 직선성을 구현하기 위해 PI 모델의 개발과 DPWM의 구동형태를 기본듀티폭 + 가변듀티의 형태로 구현하여 500ns 이하의 pulse에 대한 FET의 스위칭 불능상태를 극복하고 완전히 5ppm의 이하의 안정도와 ±400uA 영역에서 30uA/step을 실현하였다.

현재의 실험 DATA에서 보는 바와 같이 short term(30분)에서 약 80uA(4ppm)의 안정도를 유지하였으나, 이것을 1ppm 이하로 달성하기 위한 연구가 진행되어야 한다. 이를 위해서는 ADC의 Noise에 대한안정도가 확보되어야 하며 이것을 달성하기 위해서 ADC Board설계에 대한 연구가 필요하다. 또한DPWM의 분해능이 중요한데 현재 clock의 한계로 인해 15bit정도(스위칭 주파수가 50kHz일 때)가 한계이나 이것을 ADC분해능 수준의 24bit까지 올릴 수 있는 H/W의 설계가 중요한 과제이다.

그림 21. ADC Board 및 Controller Board Fig. 21. The ADC Board And The Conroller Board

#### References

- [1] Drazen Jurisic의 1일, "Low-Noise Active-RC Low-, High-, and Band-pass Allpole Filters Using Impedance Tapering", Proceedings of MEleCon 2000, Lemesos, Cyprus, (May 29-31, 2000.), pp. 591-594.

- [2] Franco, S. Design with operational amplifiers and analog integrated circuits, Book, McGraw-Hill edition, 1997.

- [3] B. Patella, "Implementation of a High Frequency, Low Power Dgital Pulse Width Modulation Controller Chip," M.S. Thesis, University of Colorado at Boulder, 2000.

- [4] San-Ho Byun, et al., "For  $\Sigma$ - $\Delta$  A/D Converter Digital Decimation Filter Design", 2007.

- [5] Majd Ghazi Y. Batarseh, "Digital Pulse Width Modulator Techniques for DC-DC Converters", 2010.

- [6] Joey White et al., "Noise Shaping in MASH Delta-Sigma Converters", 2009.

- [7] G.I. Bourdopoulus, A. Pnevmatikakis, V. Anastassopoulos and T.L.Deliyannis, "Delta-Sigma Modulators: Modeling, Design and Applications," Imperial College press, 2003.

- [8] Saman S. Abeysekera and Charayaphan Charoensak, "Efficient Realization of Sigma-Delta Kalman Lowpass Filter in Hardware Using FPGA", Hindawi Publishing Corporation, 2006.

- [9] R. D. Middlebrook, "Input Filter Considerations in Design and Application of Switching Regulators," IEEE Industry Applications Society Annual Meeting, 1976 Record, pp. 366–382.

- [10] Raymond B. Ridley, "Secondary LC Filter Analysis and Design Techniques for Current-Mode-Controlled Converters", Ieee Transaction on power electronics, Vol. 3, No. 4, October 1988.

- [11] M. Emmenegger, et al., "A Fully Digital PWM for Highest Precision Power Supplies", European Power Electronics Conference, 2001.

- [12] Ki-Hyun Park, et al., "Developing High Precision Magnet Power Supply", Journal of Korea Electrical Academic Conference, 2011. 7.

- [13] Felix Jenni, et al., "A Novel Control Concept for Highest Precision Accelerator Power Supplies".

- [14] Byung Kwon Park, "SMPS Input Filter Design", EMC Technical Center Newsletter.

- [15] Thomas Kugelstadt, "Op Amps for Everyone", Texas Instrument.

- [16] Ui Chul Rho, "Performance Analysis of 4.2MW (600VDC, 7kADC) Direct Current Pulse Power Supply", The Journal of the Korean Institute of Illuminating And Electrical Installation Engineers, The Tenth Volume, The Sixth Chapter, 1996.12, pp.73–80.

- [17] Kye-Ho Hwang, et al., "A Study on LCC Type High Frequency Resonance DC/DC Converter Applying Non-Contact Power Supply", The Journal of the Korean Institute of Illuminating And Electrical Installation Engineers, The Twenty First Volume, The Sixth Chapter, 2007.7, pp.55–64.

- [18] Suk-Jin Hong, et al., "Neutral Point Voltage Control of

Three-Level NPC Inverter using DPWM", The Journal of the Korean Institute of Illuminating And Electrical Installation Engineers, Autumn Academic Conference, 2014.11, p.96.

# ◇ 저자소개 ◇-

### 김금수(金錦洙)

1961년 8월 21일생. 인천대학교 전자공학과 졸업. 영남대학교 전기공학과 박사과정 수료. (주)LG 정보통신. (주)코오롱정보통신. 현재 (주)누리기술 대표이사.

#### **장길진**(張吉鎭)

1974년 12월 4일생. 2001년 인하대학교 자원공학과 졸업. 2005년 고려대학교 전기 전자전파공학부 졸업. 2010년 고려대학교 전기공학과 졸업 (석사). 2001~2002년 (주)LG Philips Displays. 현재 (주)누리 기술 주임 연구원.

# 김동희(金東熙)

1950년 11월 20일생. 1973년 영남대학교 전기공학과 졸업. 1987년 Kobe 대학 졸업 (박사). 1987~1989년 한국전기연구원 전력전자연구부장. 2000년 9월~2001년 2월 국립 Kyushu대 교환교수. 현재 영남 대학교 전기공학과 교수.