# Fully Wireless Neural Recording System with a 65536-Electrode Array

### **Features**

### ★ System

- Integrated 65536 titanium nitride (TiN) surface electrodes

- Wireless powered from a 13.56 MHz (F<sub>ref</sub>) Inductive Link

- o Communicates to a relay station through Ultra-wideband (UWB) radio

- Simultaneous recording from 1024 or 256 electrodes

- Constant current biphasic stimulation with ± 1.4V compliance

#### ★ Processor

Full-custom logic running at up to 108.5 MHz (F<sub>ref</sub> \* 8)

#### ★ ADC

10-bit SAR ADC running at an average 8.7 MHz (F<sub>ref</sub> \* 16/25)

### ★ Analog Front End

- Chopper stabilized pixel amplifier with programmable chopping frequency

- Effective sampling rate of 33.9 kHz (256 electrodes) or 8.5 kHz (1024 electrodes)

#### ★ Wireless Transceiver

- o 108.5 MBps uplink and 54.3 MBps downlink

- o Ultra-wide band (3.5-4.5 GHz)

### ★ Power management

60mW maximum received power

# **BISC N65K**

| Table of Contents                                      |   |

|--------------------------------------------------------|---|

| Features                                               | 1 |

| 1. Description                                         | 3 |

| Terminology                                            | 3 |

| Functional Block Diagram                               | 4 |

| BISC Headstage                                         | 5 |

| BISC Base Station                                      | 5 |

| Specifications                                         | 6 |

| Chip Die Shot                                          | 7 |

| © 2025 Kampto Neurotech, LLC Simplified Datasheet Page | 2 |

### 1. Description

BISC is an Implantable Wireless High-Density Microelectrode Array System, a state-of-the-art solution architecturally designed to facilitate a minimally invasive bridge between the brain and computational devices. This system, comprising an integrated circuit chip, a headstage, and a base station, enables users to monitor and modulate neural signals in real-time.

## **Terminology**

**BISC** refers to the complete system that contains:

BISC Chip – The implantable integrated circuit chip

BISC Headstage – The external hardware that wirelessly connects to the BISC Chip

**BISC Base Station** – The external hardware processor that connects to the BISC Headstage using an HDMI cable

BISC API – The programming interface that allows full control of the BISC system

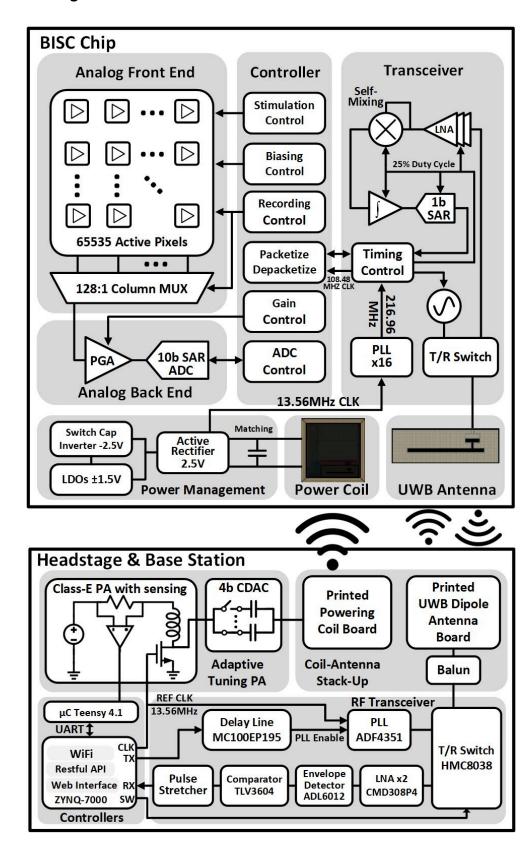

### **Functional Block Diagram**

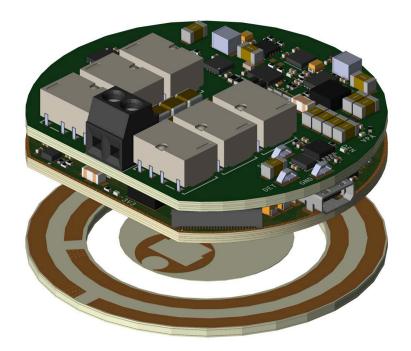

## **BISC Headstage**

**BISC Headstage without Case**

The current version of the BISC headstage has a diameter of 53mm and a height of 35mm, including the case.

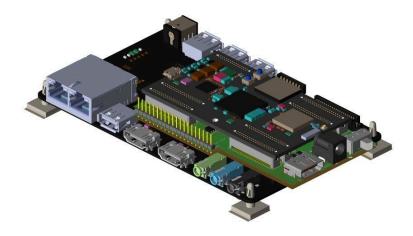

### **BISC Base Station**

**BISC Base Station without Case**

The BISC Base Station is based on the krtkl Snickerdoodle, PiSmasher, and a custom interface board.

# **Specifications**

| Implant Chip Size                | 12mm × 12mm                              |

|----------------------------------|------------------------------------------|

| Implant Chip<br>Thickness        | 250μm - 10μm                             |

| Total Channels                   | 65536                                    |

| Simultaneous Readout<br>Channels | 1024/256                                 |

| Readout Sampling<br>Rate         | 8.475/33.9kHz                            |

| Readout Resolution               | 10-bits                                  |

| Readout Gain                     | 120 - 2900V/V                            |

| Readout High Pass<br>Corner      | 5 - 120 @ 800pF Electrode<br>Capacitance |

| Readout Input Refered<br>Noise   | 5μVrms @ 1650V/V (10 -<br>8KHz)          |

| Stimulation Scheme               | Monopolar or Bipolar                     |

| Stimulation Current              | 10μΑ - 1120μΑ                            |

| Stimulation Current<br>Profile   | Biphasic                                 |

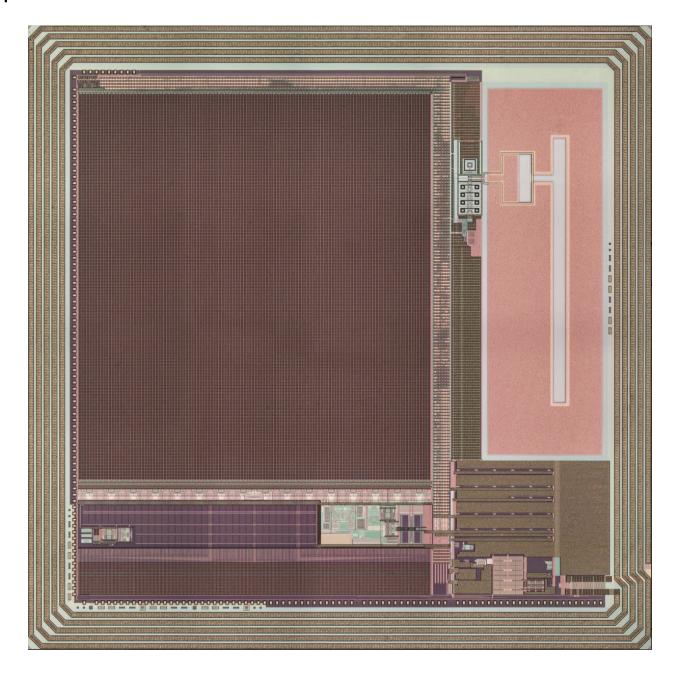

# **Chip Die Shot**